先进制程工艺进度缓慢的情况下,多芯片整合封装成了半导体行业的大趋势,各家不断玩出新花样。

ISSCC 2023国际固态电路大会上,AMD提出了多种新的整合封装设想,其中之一就是在CPU处理器内部,直接堆叠DRAM内存,而且是多层堆叠。

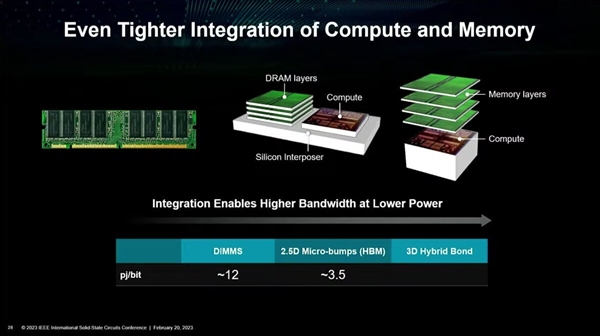

一种方式是CPU计算模块、DRAM内存模块,并排封装在硅中介层上,而另一种方式就是在计算模块上方直接堆叠内存模块,有点像手机SoC。

AMD表示,这种设计可以让计算核心以更短的距离、更高的带宽、更低的延迟访问内存,而且能大大降低功耗,2.5D封装可以做到独立内存功耗的30%左右,3D混合键合封装更是仅有传统的1/6。

如果堆叠内存容量足够大,主板上的DIMM插槽甚至都可以省了。

当然,AMD的这种设想仅面向服务器和数据中心领域,桌面上不会这么做,否则就无法升级了。

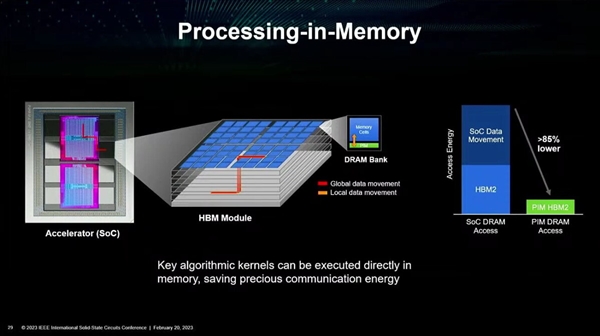

AMD甚至考虑在Instinct系列加速卡已经整合封装HBM高带宽内存的基础上,在后者之上继续堆叠DRAM内存,但只是一层,容量不会太大。

这样的最大好处是一些关键算法内核可以直接在整合内存内执行,而不必在CPU和独立内存之间往复通信传输,从而提升性能、降低功耗。

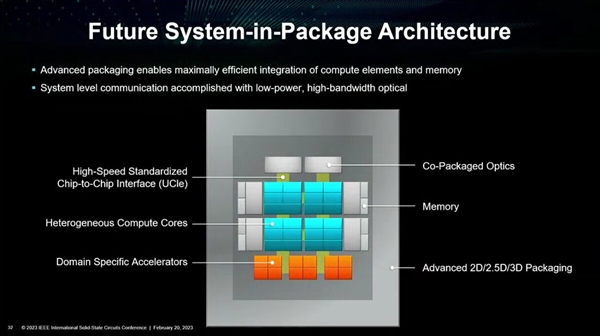

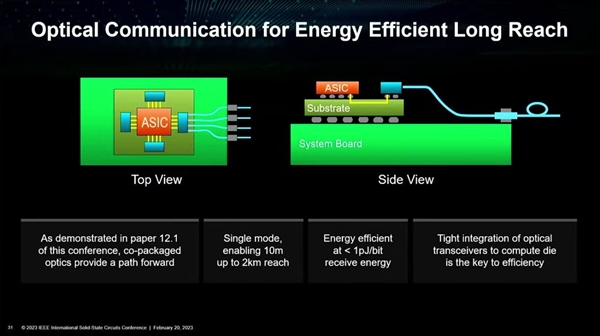

另外,AMD还设想在2D/2.5D/3D整合封装芯片的内部,除了CPU+GPU混合计算核心,还集成更多模块,包括内存、统一封装光网络通道物理层、特定域加速器等等,并引入高速标准化的芯片间接口通道(UCIe)。

尤其是引入光网络通道,可以大大简化网络基础架构。

登录可免费下载软件

VIP可高速下载,支持百度、123网盘、蓝奏网盘等全站资源。

永久VIP可加入专属群,享受群内福利,享受1对1服务。

非VIP会员类型

分普通会员、黄金会员、钻石会员,不同会员的下载次数各不相同。

可通过积分兑换及签到获取积分。

联系客服

如链接失效或有其他问题,请联系客服微信:

diannaodiyquan 或 diannao10zv或者diy10zv

(备注:“电脑DIY圈”以防封号)

免责声明

1. 软件全部来源于网络,如有侵权请联系客服。

2. 本站一切资源不代表本站立场,并不代表本站赞同其观点和对其真实性负责。

3. 本站一律禁止以任何方式发布或转载任何违法的相关信息,访客发现请向站长举报。

4. 本站资源大多存储在云盘,如发现链接失效,直接跟帖催更我们会第一时间回复。

暂无评论内容